1. はじめに

私たちが日々使うスマートフォンやコンピューターの中には、数十億個ものトランジスタが詰め込まれた半導体チップが入っています。これらのチップは、髪の毛の太さの何千分の一というナノメートル単位の精密さで製造されており、その製造工程では「検査」が極めて重要な役割を果たしています。

半導体製造における検査工程では、テスト画像と参照画像を正確に重ね合わせる「画像アライメント(位置合わせ)」 という技術が不可欠です。これは、まるで2枚の半透明の写真を完璧に重ね合わせるような作業で、わずかなズレも許されません。なぜなら、アライメントが不正確だと、実際には存在しない「欠陥」を誤検出したり、本物の欠陥を見逃したりしてしまうからです。

しかし、従来のアライメント手法には深刻なジレンマがありました。アルゴリズムの感度を下げると誤った位置に合わせてしまう「誤アライメント」が発生し、逆に感度を上げすぎると製造プロセスのわずかな変化で頻繁にアライメントが失敗してしまうのです。

本記事では、この課題を解決する革新的な技術──複数のアライメントターゲットと線形独立ベクトルを活用した新しい画像アライメント手法について、最新の特許技術と学術研究から読み解いていきます。

2. 半導体検査における画像アライメントの基礎

2-1. 検査プロセスにおけるアライメントの役割

半導体製造では、ウェーハ(シリコン基板)上に数百もの工程を経て回路パターンを形成します。各工程の後には、欠陥がないかを確認するための検査が行われます。

この検査の基本的な流れは以下の通りです。

- テスト画像の撮影:検査対象のウェーハを光学顕微鏡やSEMで撮影

- 参照画像との比較:正常なパターンの参照画像と比較

- 差分画像の生成:2つの画像を引き算して差分を抽出

- 欠陥検出:差分画像から異常部分を検出

この流れの中で、ステップ2の「比較」の前に正確なアライメントが必要になります。もし画像が1ピクセルでもずれていれば、正常な部分が「差分」として検出され、誤った欠陥として報告されてしまいます。

2-2. アライメントサイトとカーネル画像

従来の手法では、アライメントサイト(alignment site) と呼ばれる特定の位置を1箇所選定し、その画像をカーネル画像として記録します。実際の検査時(ランタイム)には、このカーネル画像とランタイム画像を照合してアライメントを行います。

しかし、この「単一アライメントサイト」方式には重大な問題がありました。

- 誤アライメントのリスク:感度を下げすぎると、本来とは異なる場所に一致してしまう

- アライメント失敗の頻発:感度を上げすぎると、わずかなプロセス変動で失敗する

- アライメントサイトの損傷:サイトが欠損や損傷した場合に対処できない

2-3. 従来手法の限界:感度調整のジレンマ

従来のアルゴリズム開発では、画像処理によってランタイム画像をセットアップ時のカーネル画像に近づける試みが行われてきました。例えば、

- コントラスト強調:特定のパターンを強調

- 周波数フィルタリング:不要な成分を除去

- パターン抽出:特徴的な形状を抽出

しかし、このような「感度を下げる」処理を行いすぎると、画像が大きく変化してしまい、本来とは異なるアライメントサイトに一致してしまう可能性があります。これが「誤アライメント」であり、後続の「プレマップ」や「ピクセル-デザインアライメント(PDA)」の処理が中断される原因となります。

逆に、「感度を高く保つ」と、製造プロセスの正常な変動(温度、湿度、材料のロット差など)によってもアライメントが失敗し、検査が即座に中断されてしまいます。

このジレンマを解決する新しいアプローチが求められていました。

3. 特許から見る技術革新:複数ターゲットアライメント

3-1. 複数アライメントターゲットと線形独立ベクトル(US20220327796A1)

2022年に公開された特許「US20220327796A1 – Salient feature point based image alignment」では、複数のアライメントターゲットを活用する革新的な手法が提案されています。

この技術の核心は、3つ以上のアライメントターゲットを選定し、それらの位置ベクトルが「線形独立」であることを条件とする点です。線形独立とは、簡単に言えば「どのベクトルも他のベクトルの組み合わせで表現できない」という性質で、これにより各ターゲットが独立した情報を提供します。

技術の特徴:

- 複数候補からの投票方式:各ターゲットがそれぞれ参照位置の座標を計算し、最終的にそれらを統合

- 冗長性の確保:1つのターゲットが損傷していても、他のターゲットで補完可能

- 誤アライメントの抑制:複数の独立した情報源からの一致が必要なため、誤った位置への一致が起こりにくい

この手法により、従来の「単一ターゲット・単一アルゴリズム」の限界を突破し、ロバスト性と精度の両立が実現されています。

特許URL:https://patents.google.com/patent/US20220327796A1/en

3-2. ピクセル位置補正ループを用いた欠陥位置決定(US11049745B2)

2021年に登録された特許「US11049745B2 – Defect-location determination using correction loop for pixel alignment」では、ピクセルレベルの位置補正ループを導入した技術が開示されています。

この技術では、以下のプロセスが実行されます:

- プレ検査アライメント:検査前にウェーハ全体のアライメントを実施

- 第1スワス(swath)実行:最初の画像取得領域をスキャン

- ピクセル補正ループ:画像間のわずかなピクセルずれを反復的に補正

- 欠陥位置の高精度決定:補正後の座標系で欠陥位置を特定

この手法は、ダイナミックに変化する製造環境に対応できる柔軟性を持ち、特に大面積ウェーハの高速検査において威力を発揮します。

特許URL:https://patents.google.com/patent/US11049745B2/en

3-3. 統合的アライメントシステム(US11231376B2)

2022年に登録された「US11231376B2 – Method for semiconductor wafer inspection and system thereof」は、光学検査とSEM検査を統合したアライメントシステムを提案しています。

この特許の革新性は、

- マルチモーダル画像の統合:光学顕微鏡とSEMの画像を同一座標系で処理

- 階層的アライメント:粗い位置合わせから微細な位置合わせへ段階的に精度を向上

- リアルタイム補正:検査中の熱膨張やステージドリフトを動的に補正

これにより、異なる検査装置間でのデータ連携が可能になり、より包括的な欠陥分析が実現されています。

特許URL:https://patents.google.com/patent/US11231376B2/en

4. 応用分野と実用化

4-1. 先端ロジック半導体製造(7nm以下)

最先端の半導体製造では、7nm、5nm、さらには3nmノードといった極微細プロセスが実用化されています。これらのプロセスでは、パターンのサイズが光の波長よりも小さいため、従来の光学検査だけでは不十分です。

複数ターゲットアライメント技術は、EUV(極端紫外線)リソグラフィー後の検査において特に重要です。EUVプロセスでは、わずかなアライメント誤差が歩留まりに直結するため、サブナノメートル精度のアライメントが求められます。

4-2. 3D-NAND・HBMなど3次元構造デバイス

近年、メモリデバイスは平面構造から3次元構造へと進化しています。3D-NANDフラッシュメモリやHBM(High Bandwidth Memory)では、数十層から100層以上の積層構造を持ちます。

これらのデバイスの検査では、各層のアライメントを正確に追跡する必要があります。複数ターゲット方式により、積層された各層の微小なずれを検出し、製造プロセスの改善にフィードバックすることが可能になります。

4-3. AIとディープラーニングの統合

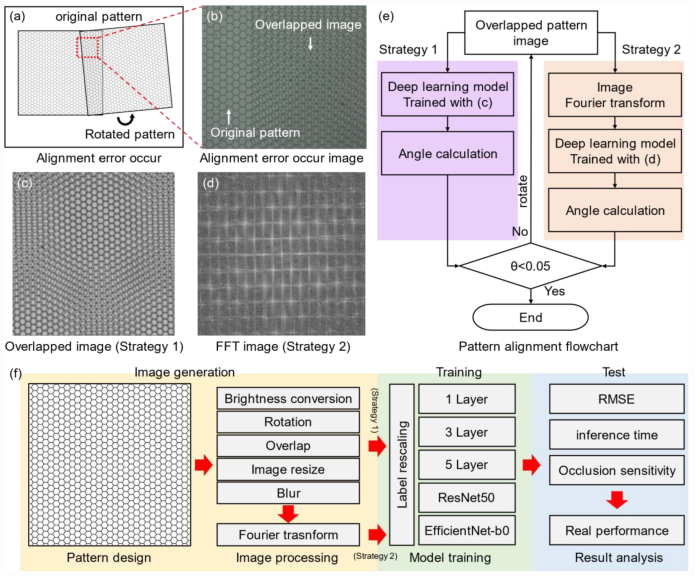

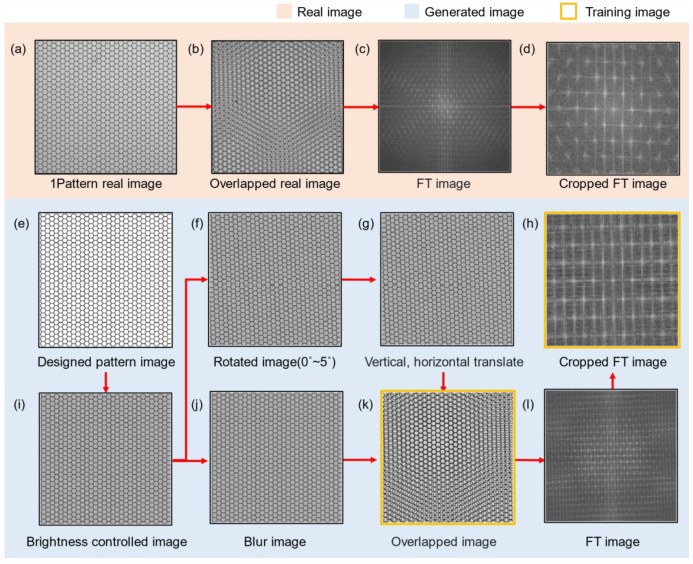

最新の研究では、アライメント技術にディープラーニングを統合する試みが進んでいます。2024年のSpringer論文では、フーリエ変換画像を用いた畳み込みニューラルネットワーク(CNN) により、アライメント誤差を0.018度のRMSEで予測できることが示されています。

このAI統合により、

- アライメントマークなしでのアライメントが可能に

- リアルタイム角度予測により処理時間を大幅短縮

- 様々なパターン形状に自動適応

という利点が得られます。

5. 課題と展望

5-1. 現在の技術的課題

複数ターゲットアライメント技術は大きな進歩を遂げていますが、いくつかの課題も残されています。

計算コストの増加

複数のターゲットを同時に処理するため、従来の単一ターゲット方式と比べて計算量が増加します。特にリアルタイム検査が求められる量産ラインでは、処理速度の最適化が重要です。

ターゲット選定の自動化

線形独立なベクトルを持つターゲットを自動的に選定するアルゴリズムの開発が必要です。現状では、セットアップ時に人間のオペレーターが適切なターゲットを選ぶ必要があり、完全な自動化には至っていません。

新しいパターン形状への対応

次世代デバイスでは、従来とは異なる新しいパターン形状(例:FinFET、Gate-All-Around FET)が登場しています。これらの複雑な3次元構造に対応したアライメント手法の開発が求められています。

5-2. 研究の最前線

学術界では、さらなる革新が進んでいます。

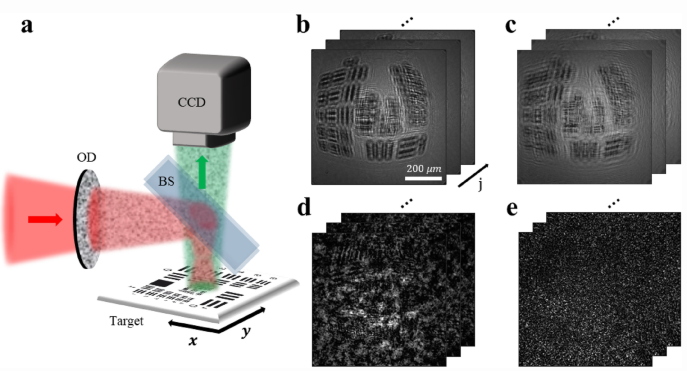

2024年のNature Communications論文では、メタサーフェスアライメントマークを用いて、離れた2つの物体間の3次元ミスアライメントをサブナノメートル精度で測定する技術が報告されています。これは、ウェーハtoウェーハボンディングなど、より高度な3次元集積技術への道を開くものです。

また、2025年のNature Scientific Reports論文では、レンズフリー反射型トポグラフィにより、広視野かつ高解像度(1.7μm)でのウェーハ検査が実現されています。この技術は、スペックル照明とCNNベースの画像再構成を組み合わせることで、従来のレンズベースシステムの制約を超えています。

5-3. 未来の展望:自律的検査システムへ

今後の半導体検査は、自律的な判断と適応が可能なシステムへと進化していくと予想されます。

予測される技術発展

- 完全AI駆動のアライメント:人間の介入なしで最適なアライメント戦略を自動選択

- 予測的メンテナンス:アライメント精度の経時変化から装置の劣化を予測

- デジタルツイン統合:実際の製造ラインと仮想空間をリンクし、最適なアライメントパラメータをシミュレーション

- 量子センシングの応用:量子効果を利用した超高精度位置測定

これらの技術により、2030年代には1nmノード以下のプロセスにおいても、高い歩留まりでの大量生産が可能になると期待されています。

あわせて読みたい

検査技術の高度化は、チップレット化・標準化(UCIeなど)の流れとも表裏一体です。

6. 結論

半導体検査における画像アライメント技術は、一見地味に見える「写真合わせ」の技術ですが、実は最先端チップ製造を支える重要な基盤技術です。

本記事で紹介した複数ターゲットアライメント手法は、従来の「単一ターゲット・感度調整のジレンマ」を解決し、誤アライメントの抑制とロバスト性の両立を実現しました。線形独立ベクトルという数学的概念を巧みに活用することで、複雑な製造環境下でも安定した検査が可能になっています。

さらに、AIとディープラーニングの統合により、アライメントマークなしでのリアルタイム処理という、かつては不可能と思われた目標が現実のものとなりつつあります。

半導体技術の進化は止まることを知りません。より微細なパターン、より複雑な3次元構造、そしてより高速な製造──これらすべての実現には、画像アライメント技術のさらなる進化が不可欠です。この「見えない技術」が、私たちの未来のデジタル社会を支え続けるのです。

参考文献

テーマに近い関連する特許文献

- US20220327796A1 – Salient feature point based image alignment (KLA Corporation, 2022)

https://patents.google.com/patent/US20220327796A1/en - US11049745B2 – Defect-location determination using correction loop for pixel alignment (KLA Corporation, 2021)

https://patents.google.com/patent/US11049745B2/en - US11231376B2 – Method for semiconductor wafer inspection and system thereof (ASML Netherlands, 2022)

https://patents.google.com/patent/US11231376B2/en

記事を作成するにあたり参考にした文献

- Nature Scientific Reports (2025) – “Enhancing thin-film wafer inspection with a multi-sensor array and spectrometry”

https://www.nature.com/articles/s41598-025-23640-5 - IOP Science, International Journal of Extreme Manufacturing (2022) – “Optical wafer defect inspection at the 10 nm technology node and beyond”

https://iopscience.iop.org/article/10.1088/2631-7990/ac64d7/meta - Springer, Journal of Intelligent Manufacturing (2024) – “Simulation of semiconductor wafer dicing induced faults on chips”

https://link.springer.com/article/10.1007/s10845-024-02559-0 - Nature Scientific Reports (2023) – “Ranking routes in semiconductor wafer fabs”

https://www.nature.com/articles/s41598-023-39187-2 - Nature Communications (2024) – “3D alignment of distant patterns with deep-subwavelength precision”

https://www.nature.com/articles/s41467-024-53219-z - Nature Scientific Reports (2024) – “Lens-free reflective topography for high-resolution wafer inspection”

https://www.nature.com/articles/s41598-024-59496-4 - Springer, Journal of Intelligent Manufacturing (2024) – “Deep learning-based rotational alignment technique using image generation and Fourier Transform”

https://link.springer.com/article/10.1007/s10845-024-02549-2

※ 記事は公開されている特許情報および学術研究をもとに作成しています。図版は各出典元から引用しています。

コメント